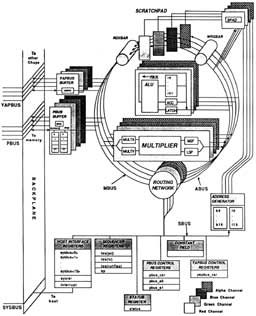

This is a picture of the 4 slot P-II. It could have two Channel Processors, or Chaps.

Each Chap is 4 way parallel (RGBA) image computer, as shown below.

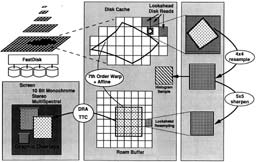

We built a larger chassis, which could hold 9 cards (4 Chaps, 2 Video processors, 2 Off Screen Memory (OSM) cards, and an Overlay Board for the Postscript Windowing System (NeWS).

We implemented the core image pipeline routines in Chap assembler.

We integrated very early model Maximum Strategy RAIDs. Huge cabinets which held 3GB, but were "fast" at 8 MB/sec.

We added an Overlay board running a Network Extensible Windowing System, (NeWS). The extensions we added were to control the image pipeline for roaming, image comparison, and stereo image viewing. The PII-9 was the imaging engine for a Unix host.